삼성전자, 미국서 '삼성 파운드리 포럼 2018 '개최...3나노 공정 공개

내년 상반기 7나노 생산 목표

3나노에 MBCFETTM 최초 적용..성능향상

3나노에 MBCFETTM 최초 적용..성능향상

삼성전자가 지난 22일 미국 산타 클라라 메리어트 호텔에서 '삼성 파운드리 포럼 2018'을 개최하고 14나노부터 3나노까지의 반도체 공정 로드맵을 공개했다고 23일 밝혔다.

삼성 파운드리 포럼은 팹리스 업계 고객사, 파트너사, 애널리스트 등을 초청해 매년 확장되는 파운드리 시장 규모와 차별화된 기술력을 바탕으로 향후 파운드리 사업 비전을 제시하는 자리다.

이번 행사에서 삼성전자는 주력 양산 공정인 14·10나노 공정, 극자외선노광장비(EUV·Extreme Ultra Violet)를 활용한 7·5·4나노 공정에서 새롭게 3나노 공정까지의 로드맵을 공개했다.

7나노(nm·나노미터, 1나노는 10억분의 1미터) LPP(Low Power Plus) 공정은 EUV 장비를 적용한 최초 로직 공정으로 올 하반기 시험생산, 내년 상반기 생산 목표로 개발 중이다.

5나노 LPE(Low Power Early)는 스마트 스케일링(Smart Scaling)으로 7나노 대비 면적 및 소비전력이 축소된 것이 특징이다. 스마트 스케일링은 미세회로의 선폭을 줄여서 설계 환경을 최적화해 더 작은 면적의 칩 설계 가능하도록 하는 기술이다.

4나노 LPE/LPP(Low Power Early/Plus)는 핀펫(Fin Field Effect Transistor·FinFET)을 적용한 마지막 공정으로 5나노에서 이지 마이그레이션(Easy migration)을 지원한다. 지난 2014년부터 등장한 핀펫 공정은 기존 평면(2D) 구조의 한계를 극복하기 위해 도입된 입체(3D) 구조의 공정 기술이다.

3나노 GAAE/GAAP(Gate-All-Around Early/Plus)는 차세대 트랜지스터 구조인 MBCFETTM을 최초 적용, 게이트 컨트롤 개선으로 성능이 대폭 향상됐다. MBCFETTM (Multi Bridge Channel FET)은 FinFET 구조의 크기 축소와 성능 향상의 한계를 극복한 GAAFET(Gate All Around FET) 기술의 삼성전자 독자 브랜드다.

이밖에 삼성전자는 이번 행사에서 향후 광범위한 첨단 공정 개발과 설계 인프라, SAFE(Samsung Advanced Foundry Ecosystem)의 지속 확장에 대해서도 발표했다.

배영창 삼성전자 파운드리사업부 전략마케팅팀장(부사장)은 “지난 한 해 EUV 공정을 적용한 포트폴리오를 강화하는데 주력해왔다”며 “향후 GAA(Gate-All-Around)구조를 차세대 공정에 적용함으로써 단순히 기술 리더십을 선도할 뿐 아니라 좀 더 스마트하며 기기 간의 연결성을 강화한 새로운 시대를 열어갈 수 있으리라 기대한다”고 말했다.

한편 ‘삼성 파운드리 포럼 2018’은 이번 미국 포럼을 시작으로 6월 중국 상하이, 7월 한국 서울, 9월 일본 도쿄, 10월 독일 뮌헨으로 이어질 예정이다.

©(주) 데일리안 무단전재 및 재배포 금지

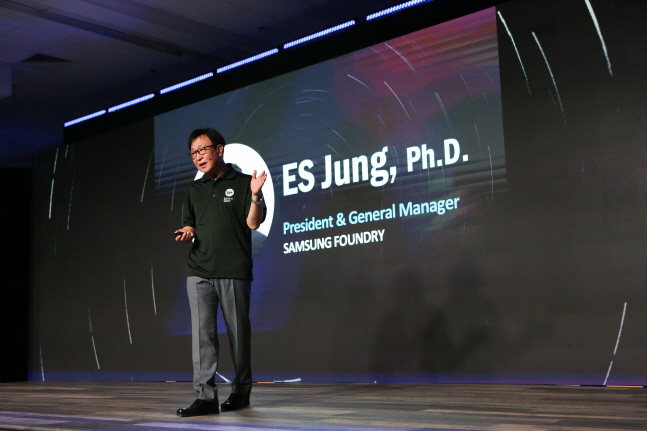

정은승 삼성전자 파운드리사업부장(사장)이 22일(현지시간) 미국 캘리포니아주 산타클라라 메리어트호텔에서 개최된 '삼성 파운드리포럼 2018'에서 파운드리 사업전략과 첨단 공정 로드맵을 발표하고 있다.ⓒ삼성전자

정은승 삼성전자 파운드리사업부장(사장)이 22일(현지시간) 미국 캘리포니아주 산타클라라 메리어트호텔에서 개최된 '삼성 파운드리포럼 2018'에서 파운드리 사업전략과 첨단 공정 로드맵을 발표하고 있다.ⓒ삼성전자